Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

[ad_1]

Tessent Multi-die software program answer will help simplify crucial design-for-test (DFT) duties for advanced built-in circuits (ICs) primarily based on 2.5D and 3D architectures.

The search for growing compact and energy-efficient gadgets has led designers to create extra power-efficient and power-dense ICs. These next-generation gadgets are made potential by using 2.5D and 3D architectures that join dies vertically (3D IC) or side-by-side (2.5D) in order that they behave as a single machine. To simplify the method, Siemens Digital Industries Software program has launched a brand new software program answer referred to as Tessent Multi-die software program answer.

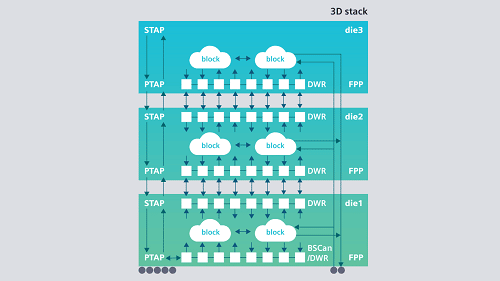

The speedy adoption and deployment of designs that includes densely packed dies in 2.5D and 3D gadgets have elevated the IC take a look at complexity. To sort out this downside the Tessent Multi-die software program answer can generate die-to-die interconnect patterns and allow package-level exams utilizing the Boundary Scan Description Language (BS DL). The brand new software program can seamlessly work with different software program instruments utilizing an built-in Tessent platform, thus lowering take a look at time as much as 4X.

In line with the corporate, the Tessent Multi-die software program is likely one of the most complete DFT automation options for extremely advanced DFT duties related to 2.5D and 3D IC designs. The software program can be utilized with different software program from the Tessent sequence similar to Tessent TestKompress Streaming Scan Community software program and Tessent IJTAG software program, which optimize DFT take a look at sources for every block with out concern for impacts to the remainder of the design, thereby streamlining DFT planning and implementation for the two.5D and 3D IC period. This software program permits designers to quickly generate IEEE 1838-compliant {hardware} that includes 2.5D and 3D IC architectures.

“As the bounds of conventional 2D IC design approaches change into more and more clear over time, extra design groups are leveraging the facility, efficiency and type issue benefits that 2.5D and 3D IC architectures can ship. However deploying these superior schemes in new design begins with out first establishing a DFT technique that acknowledges the inherent challenges these architectures current can elevate prices and undermine aggressive timelines,” stated Laurie Balch, president and analysis director for Pedestal Analysis. “Nevertheless, by evolving DFT know-how to maintain tempo with the speedy adoption of multi-dimensional designs, EDA distributors can play a key function in additional enabling world, mainstream adoption of two.5D and 3D architectures.”

Key options

• Dramatically speeds and simplifies crucial DFT planning and implementation duties for next-generation ICs primarily based on 2.5D and 3D architectures

• Allows the speedy era of IEEE 1838 compliant {hardware} for 3D IC architectures

• Extracts a single Boundary Scan Description Language (BSDL) for bundle degree and generates patterns

• Extracts die-to-die BSDL and generates boundary-scan-based inter-die patterns

• Helps IEEE 1838 versatile parallel port (FPP) by leveraging the packetized information supply capabilities of the Tessent Streaming Scan Community (SSN) , which optimize DFT take a look at sources for every block with out concern for impacts to the remainder of the design

• Capacity to stick and help a number of totally different requirements like IEEE 1687 and IEEE 1149.1

• Seamless integration with different Tessent merchandise utilizing an built-in Tessent platform

[ad_2]